## Integration of vertical InAs nanowire arrays on insulator-on-silicon for electrical isolation

Shadi A. Dayeh, Peng Chen, Yi Jing, Edward T. Yu, <sup>a)</sup> S. S. Lau, <sup>b)</sup> and Deli Wang<sup>c)</sup> Department of Electrical and Computer Engineering, University of California, San Diego, 9500 Gilman Drive, La Jolla, California 92093-0407, USA

(Received 1 September 2008; accepted 10 October 2008; published online 20 November 2008)

Vertical and electrically isolated InAs nanowires (NWs) are integrated with Si in a technique that bypasses structural defects and transport barriers at the Si–III–V NW interface. Smart-cut® technique is used to transfer a thin InAs layer onto SiO<sub>2</sub>/Si and is subsequently used for ordered organometallic vapor phase epitaxy of InAs NWs. The InAs layer in the regions between the InAs NWs is etched resulting in ordered, vertical, and electrically isolated InAs NW arrays. This transfer and fabrication technique enables heteroepitaxy of three dimensional III–V structures on Si and allows the realization of vertical devices with unprecedented control over their architectures. © 2008 American Institute of Physics. [DOI: 10.1063/1.3013566]

Semiconductor nanowires (NWs) have allowed the realization of several key components for electronic and photonic systems including surround-gate field-effect transistors (FETs), 1,2 light emitting diodes, 3 photodetectors, 4 and waveguides.<sup>5</sup> However, for integrated functional systems, growth or post-growth assembly of NWs at specified locations is necessary but has remained challenging. NW growth at predetermined locations suitable for direct device integration is desired. Typically, e-beam lithography or nanoimprint lithography is utilized to pattern growth seeds at specified locations followed by NW array growth. These arrays can then be used for device fabrication, such as vertical wraparound gate FETs; 1,2,7-9 however, the presence of the underlying semiconducting substrate precludes electrical isolation and individual addressability of single NWs. NW growth at predetermined locations has also been achieved on (111) sidewall stripes etched on (110) substrates—resulting in the so-called NW bridges. 10-12 Individual addressability may be achieved with this technique but with bulky contacts and added complexity in device fabrication. Postgrowth assembly of individual NWs as well as NW arrays has also been demonstrated. Examples of these are fluidic alignment, 13 electric-field manipulation, 14 Langmuir–Blodgett alignment, 15 and sequential printing of NWs on various types of host substrates. 16,17 While these approaches may be suitable for heterogeneous integration that requires low temperature processing, such as integration to flexible substrates, 16 they may not be suitable for practical fabrication of dense and high performance devices that can compete with current planar devices. It has been argued that future technology nodes should make use of the advancement in mainstream Si technology, and thus, promising high performance devices should be integrated to Si substrates. Demonstrated growth of III-V NWs on Si 18-21 may not represent the ideal candidates for future technology nodes due to the presence of potential barriers at the III-V/Si interface and lack of the ability for addressing single NW devices for multifunctions per chip. In this work, we demonstrate a nonconven-

tional integration scheme for III–V NWs to Si substrates that allows vertical integration, electrical isolation, and individually addressable III–V NWs on Si suitable for three dimensional circuit applications.

III–V NW integration to Si substrates as described here is achieved by a layer transfer technique that combines hydrogen ion implantation and wafer bonding, known as the ion-cut or Smart-cut® process. This approach has been widely used for producing silicon-on-insulator (SOI) wafers. Recently, using this method, III–V materials have been integrated to Si substrates for application in high performance III–V devices on Si substrates, such as waveguide photodetectors and dual junction solar cells. To perform growth of electrically isolated III–V NWs on Si substrates, the Smart-cut® technique is an ideal candidate that allows the formation of an epitaxial III–V base for NW growth on insulator-on-Si.

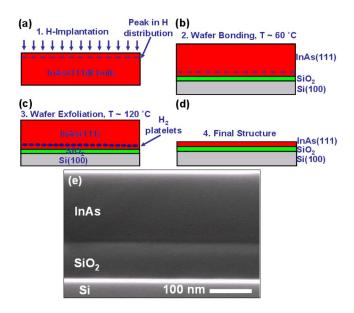

For these studies, 2 in. InAs (111)B wafers were implanted with H ions at 20 keV with a dose of 5  $\times 10^{16}$  cm<sup>-2</sup> at -15 °C. For high growth yield of vertically aligned InAs NWs normal to the substrate surface, InAs (111)B surfaces are preferred. The projected range of hydrogen is ~180 nm below the surface. After ion implantation [Fig. 1(a)], the InAs (111)B wafer is cut into 1 ×1 cm<sup>2</sup> chips for wafer bonding. An implanted InAs chip and a Si (100) wafer coated with a thermally grown oxide layer are cleaned using organic solutions and activated using O<sub>2</sub> plasma at 150 W for 30 s.<sup>27</sup> The two pieces are then put into contact at room temperature in air, and the bonded pair is annealed on a hot plate at a temperature of  $\sim 60-70$  °C for  $\sim 10$  h to increase the bonding strength. The temperature is then raised to  $\sim$ 120  $^{\circ}$ C to achieve hydrogen-induced layer exfoliation. The accumulation of trapped hydrogen around the projected range facilitates the formation and development of hydrogen platelets, as illustrated in Fig. 1(c), that eventually lead to exfoliation of the bonded structure near the projected depth [Fig. 1(d)]. The final structure after layer transfer is shown in the cross-sectional field-emission scanning electron microscope (FE-SEM) image of Fig. 1(e) consisting of a  $\sim$ 180 nm thick InAs layer atop a  $\sim$ 70 nm SiO<sub>2</sub> layer on Si. This transferred structure is annealed at 450 °C in air for 1 h under an external applied pressure of

a)Electronic mail: ety@ece.ucsd.edu.

b) Electronic mail: lau@ece.ucsd.edu.

c)Electronic mail: dwang@ece.ucsd.edu.

FIG. 1. (Color online) [(a)–(d)] Process flow for ion implantation induced transfer layer to SiO2/Si. (e) Cross-sectional FE-SEM image of the transferred InAs layer to SiO<sub>2</sub>/Si.

1 MPa to further increase the bonding strength for subsequent epitaxial growth.

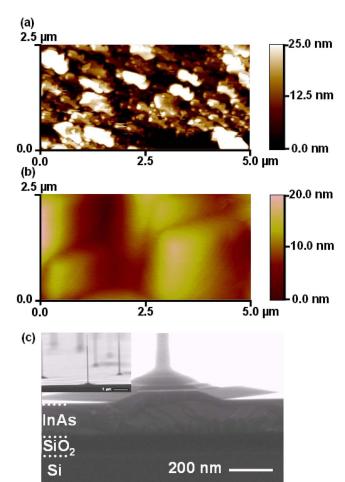

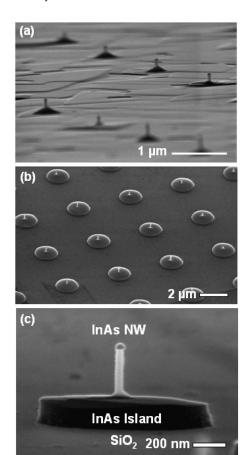

The spread in the distribution of the implanted hydrogen (i.e., straggle;  $\sim$ 65 nm from SRIM simulations)<sup>28</sup> results in a rough surface morphology directly after the ion-cut procedure. In addition, the hydrogen implantation process results in a damaged crystal structure at the surface.<sup>29</sup> Such damaged and rough surface is not suitable for NW growth due to the presence of abundant nucleation sites that lead to surface growth instead of NW growth. Figure 2(a) shows an atomic force microscope (AFM) topograph of the InAs surface after layer transfer to SiO<sub>2</sub>/Si with a rms surface roughness of ~9 nm. When 40 nm diameter Au colloids were deposited atop this surface and organometallic vapor phase epitaxy (OMVPE) growth was performed at conditions optimized for InAs NW growth on InAs (111)B surfaces, <sup>26</sup> no NW growth was observed, indicating that surface modification/repair is necessary. To obtain a surface suitable for NW growth, the samples were wet etched in a HC1:H<sub>2</sub>O<sub>2</sub>:H<sub>2</sub>O (100:1:100) solution, followed by thin film OMVPE growth leading to a planarized InAs surface with reduced rms surface roughness of  $\sim 3$  nm, as shown in the AFM topograph in Fig. 2(b). 40 nm diameter Au colloids were deposited atop the transferred InAs layer and OMVPE growth was performed for 6 min leading to efficient NW growth. Figure 2(c) shows a crosssectional FE-SEM image at the base of an InAs NW grown on InAs/SiO<sub>2</sub>/Si. This demonstrates that etching the damaged InAs layer and planarization of the transferred InAs surface enable the growth of InAs NWs on ion-cut transferred layers. In addition, ordered InAs NW growth is also feasible on such layers. For this purpose, e-beam lithography was used to pattern a double layer of positive e-beam resist (MMA/PMMA) followed by e-beam evaporation and lift off for a 25 nm thick Au layer. Consequent OMVPE growth on these patterned substrates leads to ordered InAs NWs grown on InAs/SiO<sub>2</sub>/Si with  $\sim$ 60 nm diameter and 4  $\mu$ m spacing, as shown in the FE-SEM image of Fig. 3(a).

For practical device integration into functional systems, electrical isolation between individual NW devices is neces-

FIG. 2. (Color online) AFM topograph images of InAs on SiO<sub>2</sub>/Si (a) directly after ion-cut induced transfer and (b) after wet etching of damaged layer and OMVPE thin film growth. (c)  $85^{\circ}$  cross-sectional FE-SEM at the base of an InAs NW grown on InAs/SiO2/Si. Inset is FE-SEM image of InAs NWs grown on InAs/SiO<sub>2</sub>/Si.

sary. After growth of the NW array shown in Fig. 3(a), another e-beam lithography step is used to pattern resist disks that are aligned and centered on the InAs NW. Wet chemical etching in HCl:H2O2:H2O solution was then used to etch the InAs layer exposing the SiO<sub>2</sub> surface in the unprotected regions. Figure 3(b) shows a FE-SEM image after the InAs etching step illustrating the ordered vertical InAs NW arrays on isolated InAs disks. This constitutes the demonstration of individually addressable vertical NWs, and more importantly, this whole structure is integrated on a Si substrate. Figure 3(c) shows a close up FE-SEM image of an individual InAs NW at the center of an InAs disk on SiO<sub>2</sub> surface that is electrically isolated from other NWs in the array. The diameter of the InAs disk can be controlled by e-beam lithography and can also be used to achieve low resistance Ohmic contacts to the InAs NWs on SiO<sub>2</sub> substrate by metal evaporation directly on the InAs disks for bottom contact formation. This is necessary as InAs NWs grown directly on Si show nonlinear current-voltage (I-V) characteristics when current is injected from the NW into the Si substrate and vice versa, due to energy band-edge offsets at the InAs/Si heterointerface.<sup>30</sup> The fabrication and growth processes presented here demonstrate electrical isolation of vertical III-V NWs integrated to Si substrates with a simple geometry and physics of operation for potential devices such as vertical

FIG. 3. (a)  $85^{\circ}$  FE-SEM image of ordered InAs NW arrays grown on InAs/SiO<sub>2</sub>/Si. (b)  $45^{\circ}$  angle-view FE-SEM images of vertical and electrically isolated InAs NWs on SiO<sub>2</sub>/Si. (c) Zoom-in FE-SEM image of an InAs NW with an InAs island at its base, sitting on SiO<sub>2</sub> substrate and electrically isolated from other NWs for individual NW addressing.

III–V FETs on Si. The set back for this process is the requirement of extremely flat InAs and SiO<sub>2</sub> surfaces. The rms surface roughness for each bonding side needs to be less than 1 nm for the wafer bonding purpose.<sup>31</sup>

In summary, we presented a nonconventional scheme for III–V NW integration to Si substrates that counterparts SOI and extends its concept to high performance III–V NWs on Si. We demonstrate vertical and electrically isolated NWs—as inferred from their structure—with device architecture suitable for practical III–V NW FETs on Si. The capability of III–V NW growth on insulator on Si enables heterogeneous integration to complementary metal-oxide semiconductor (CMOS) technology for hybrid information processing.

We thank the National Science Foundation (Grant No. ECS-0506902), Office of Naval Research (N000140-5-

0149), and Sharp Laboratories of America for financial support.

- <sup>1</sup>H. T. Ng, J. Han, T. Yamada, P. Nguyen, Y. P. Chen, and M. Meyyappan, Nano Lett. **4**, 1247 (2004).

- <sup>2</sup>T. Bryllert, L.-E. Wernersson, L. E. Fröberg, and L. Samuelson, IEEE Electron Device Lett. **27**, 323 (2006).

- <sup>3</sup>F. Qian, S. Gradečak, Y. Li, C.-Y. Wen, and C. M. Lieber, Nano Lett. 5, 2287 (2005).

- <sup>4</sup>O. Hayden, R. Agarwal, and C. M. Lieber, Nature Mater. **5**, 352 (2006). <sup>5</sup>A. B. Greytak, C. J. Barrelet, Y. Li, and C. M. Lieber, Appl. Phys. Lett. **87**, 151103 (2005).

- <sup>6</sup>T. Mårtensson, P. Carlberg, M. Borgström, L. Montelius, W. Seifert, and L. Samuelson, Nano Lett. 4, 699 (2004).

- <sup>7</sup>C. Thelander, L. E. Fröberg, C. Rehnstedt, L. Samuelson, and L.-E. Wernersson, IEEE Electron Device Lett. **29**, 206 (2008).

- <sup>8</sup>J. Goldberger, A. I. Hochbaum, R. Fan, and P. Yang, Nano Lett. **6**, 973 (2006)

- <sup>9</sup>V. Schmidt, H. Riel, S. Senz, S. Karg, W. Riess, and U. Gösele, Small 2, 85 (2006).

- <sup>10</sup>K. Haraguchi, K. Hiruma, T. Kastuyama, K. Tominaga, M. Shirai, and T. Shimada, Appl. Phys. Lett. 69, 386 (1996).

- <sup>11</sup>M. S. Islam, S. Sharma, T. I. Kamins, and R. S. Williams, Nanotechnology 15, L5 (2004).

- <sup>12</sup>R. He, D. Gao, R. Fan, A. I. Hochbaum, C. Carraro, R. Moboudian, and P. Yang, Adv. Mater. (Weinheim, Ger.) 17, 2098 (2005).

- Y. Huang, X. Duan, Q. Wei, and C. M. Lieber, Science 291, 630 (2001).

X. Duan, Y. Huang, Y. Cui, J. Wang, and C. M. Lieber, Nature (London) 409, 66 (2001).

- <sup>15</sup>S. Jin, D. Whang, M. C. McApline, R. S. Friedman, Y. Wu, and C. M. Lieber, Nano Lett. 4, 915 (2004).

- <sup>16</sup>J.-H. Ahn, H.-S. Kim, K. J. Lee, S. Jeon, S. J. Kang, Y. Sun, R. G. Nuzzo, and J. A. Rogers, Science 314, 1754 (2006).

- <sup>17</sup>A. Javey, S. Nam, R. S. Friedman, H. Yan, and C. M. Lieber, Nano Lett. 7, 773 (2007).

- <sup>18</sup>T. Martensson, C. P. T. Svensson, B. A. Wacaser, M. W. Larsson, W. Seifert, K. Deppert, A. Gustafsson, L. R. Wallenberg, and L. Samuelson, Nano Lett. 4, 1987 (2004).

- <sup>19</sup>A. L. Roest, M. A. Verheijen, O. Wunnicke, S. Serafin, H. Wondergem, and E. P. A. M. Bakkers, Nanotechnology 17, S271 (2006).

- <sup>20</sup>S. G. Ihn, J. I. Song, T. W. Kim, D. S. Leem, T. Lee, S. G. Lee, E. K. Koh, and K. Song, Nano Lett. 7, 39 (2007).

- <sup>21</sup>X.-Y. Bao, C. Soci, D. Susac, J. Bratvold, D. P. R. Aplin, W. Wei, C.-Y. Chen, S. A. Dayeh, K. L. Kavanagh, and D. Wang, Nano Lett. **8**, 3755 (2008)

- <sup>22</sup>M. Bruel, Electron. Lett. **31**, 1201 (1995).

- <sup>23</sup>H. Park, A. W. Fang, R. Jones, O. Cohen, O. Raday, M. N. Sysak, M. J. Paniccia, and J. E. Bowers, Opt. Express 15, 6044 (2007).

- <sup>24</sup>M. J. Archer, D. C. Law, S. Mesropian, M. Haddad, C. M. Fetzer, A. C. Ackerman, C. Ladous, R. R. King, and H. A. Atwater, Appl. Phys. Lett. 92, 103503 (2008).

- <sup>25</sup>K. A. Dick, K. Deppert, T. Martensson, B. Mandl, L. Samuelson, and W. Seifert, Nano Lett. 5, 761 (2005).

- <sup>26</sup>S. A. Dayeh, E. T. Yu, and D. Wang, Nano Lett. 7, 2486 (2007).

- <sup>27</sup>P. Chen, Y. Jing, S. S. Lau, D. Xu, L. Mawst, T. L. Alford, C. Paulson, and T. F. Keuch, Appl. Phys. Lett. **92**, 092107 (2008).

- P. Biersack and L. Haggmark, Nucl. Instrum. Methods 174, 257 (1980).

S. Hayashi, R. Sandhu, and M. S. Goorsky, J. Electrochem. Soc. 154, H293 (2007).

- <sup>30</sup>C. Rehnstedt, T. Mårtensson, C. Thelander, L. Samuelson, and L.-E. Wernersson, Proceedings of the DRC Technical Digest, 2007, p. 135.

- <sup>31</sup>Q.-Y. Tong and U. Gosele, Semiconductor Wafer Bonding, Science and Technology (Wiley, New York, 1999).