#

# Axial SiGe Heteronanowire Tunneling Field-Effect Transistors

Son T. Le,\*<sup>,†</sup> P. Jannaty,<sup>†</sup> Xu Luo,<sup>†</sup> A. Zaslavsky,<sup>\*,†</sup> Daniel E. Perea,<sup>‡</sup> Shadi A. Dayeh,<sup>§,||</sup> and S. T. Picraux<sup>§</sup>

<sup>†</sup>Department of Physics and School of Engineering, Brown University, Providence, Rhode Island 02912, United States

<sup>‡</sup>Environmental and Molecular Sciences Laboratory, Pacific Northwest National Laboratory, Richland, Washington 99352, United States

<sup>§</sup>Center for Integrated Nanotechnologies, Los Alamos National Laboratory, Los Alamos, New Mexico 87545, United States <sup>||</sup>Department of Electrical and Computer Engineering, University of California, San Diego, California 92093, United States

**(5)** Supporting Information

**ABSTRACT:** We present silicon-compatible trigated *p*-Ge/*i*-Si/*n*-Si axial heteronanowire tunneling field-effect transistors (TFETs), where on-state tunneling occurs in the Ge drain section, while off-state leakage is dominated by the Si junction in the source. Our TFETs have high  $I_{\rm ON} \sim 2 \ \mu A/\mu m$ , fully suppressed ambipolarity, and a subthreshold slope SS ~ 140 mV/decade over 4 decades of current with lowest SS ~ 50 mV/decade. Device operation in the tunneling mode is confirmed by three-dimensional TCAD simulation. Interestingly, in addition to the TFET mode, our devices work as

standard nanowire FETs with a good  $I_{ON}/I_{OFF}$  ratio when the source-drain junction is forward-biased. The improved transport in both biasing modes confirms the benefits of utilizing bandgap engineered axial nanowires for enhancing device performance. **KEYWORDS:** SiGe heteronanowire, tunneling field effect transistor, axial heterojunction, VLS growth

odern vapor-liquid-solid (VLS) growth based on alloy catalysts has recently demonstrated the possibility of growing Si/Ge axial nanowires with controlled heterojunction abruptness,<sup>1-3</sup> combined with simultaneous control of both material composition (Si and Ge) and doping profile.<sup>4</sup> This advance opens up potential applications for electronic devices, especially for silicon-compatible tunneling field-effect transistors (TFETs). Tunneling devices can, in principle, switch more sharply and operate at lower bias than a standard FET because of their different carrier injection mechanism.<sup>5–7</sup> While in FETs the carriers are injected into the channel via gate-voltage  $V_{G}$ controlled thermal injection from the source, in TFETs carriers are injected to the channel via band-to-band tunneling (BTBT) at the drain-channel (or source-channel) junction modulated by  $V_{\rm G}$ . The high energy tail of Fermi–Dirac carrier distribution that limits the sharpness of conventional FET switching to a subthreshold swing (SS) of 60 mV/decade of current at room temperature is cut off by the bandgap in a TFET, providing the potential for sharper switching and lower SS, albeit usually over a limited range of  $V_{\rm G}$ .<sup>8,9</sup>

Because BTBT depends on semiconductor bandgap  $E_{\rm G}$  and maximum electric field  $E_{\rm MAX}$  at the tunneling junction,<sup>10</sup> the Si TFET devices demonstrated to date have suffered from low  $I_{\rm ON}$ due to the relatively large  $E_{\rm G} \sim 1.1$  eV bandgap of Si. Efforts have been made to fabricate Ge-based TFETs for its smaller bandgap and higher carrier mobilities, but experimentally the higher  $I_{\rm ON}$  typically came with a compromised SS due to inferior Ge/dielectric interfaces and higher  $I_{\rm OFF}$ .<sup>11–13</sup> Further, symmetric and scalable Si and Ge devices exhibit ambipolar response where tunneling can happen at either the source- or the drain-channel junction depending on  $V_{\rm G}$  polarity,<sup>14</sup> which is undesirable for practical applications. This can be overcome either by doping or gate alignment asymmetry<sup>11,15</sup> or, as we report here, by compositional asymmetry in our Ge-Si heteronanowires (NWs). Our hetero-NW TFETs combine high  $I_{ON}$ ~ 2  $\mu$ A/ $\mu$ m (normalized to wire diameter) with low  $I_{OFF}$  ~ 40  $pA/\mu m$ , since tunneling happens in the Ge and Si sections of the NW in the on and off states, respectively, good trigate electrostatic control (compared to planar TFETs), an average SS of ~140 mV/decade over 4 orders of drain current  $I_D$  (with lowest SS of ~50 mV/decade),  $I_{\rm ON}/I_{\rm OFF}$  ratio of ~10<sup>5</sup>, and suppression of ambipolar behavior. Three-dimensional Sentaurus TCAD as well as experimentally demonstrated ohmic contact behavior confirms that the operating mechanism is  $V_{G}$ modulated BTBT current at the Ge-Si heterojunction, rather than gate-assisted Schottky barrier injection at the contact metal-Si interface as has been previously reported in axial Ge/Si hetero-NWs.<sup>16</sup> Finally, in addition to the TFET mode under reverse source-drain bias, our device can also operate as a conventional NW FET under forward source-drain bias, where instead of interband tunneling, V<sub>G</sub> modulates the thermal injection barrier under the gate.

The axial p-Ge/*i*-Si/n-Si hetero-NWs were grown by the VLS method using 50 nm Au colloid nanoparticles on Ge(111) substrates in a cold-walled chemical vapor deposition (CVD) reactor and build on our growth results that demonstrated the

ACS Publications © 2012 American Chemical Society

Received:August 28, 2012Revised:October 15, 2012Published:October 25, 2012

first 100% composition modulated Ge/Si axial hetero-NWs.<sup>17,18</sup>  $GeH_4$  (30% in H<sub>2</sub>) and SiH<sub>4</sub> (50% in H<sub>2</sub>) were used as the Ge and Si source precursors and B<sub>2</sub>H<sub>6</sub> and PH<sub>3</sub> (both at 100 ppm in  $H_2$ ) as *p*- and *n*-type dopants, respectively. The Ge(111) NW growth was initiated by nucleation at 380 °C for 3 min followed by growth at 280 °C for 30 min. Following growth of p-Ge segment, in situ catalyst alloying was accomplished by flowing vapor-phase trimethylgallium (TMGa) from a bubbler line for  $\sim$ 7 s at 380 °C. The TMGa provided a source of Ga to form a  $Au_{1-r}Ga_r$  catalyst alloy in situ during growth where an increase in heterojunction abruptness has been shown with increasing Ga composition (x).<sup>1</sup> TMGa was then removed, and the temperature was raised to 495 °C. An i-Si segment was then grown for 15 min, followed by n-Si for 30 min. A total pressure of 2 Torr was maintained throughout the Ge growth and alloy formation, while the total pressure of 0.5 Torr was maintained for the Si growth. A significant fraction of the hetero-NWs developed a kink at the Ge/Si junction, which could be avoided by optimizing the growth conditions,<sup>17</sup> but actually proves helpful for prototype TFET fabrication. The wire diameter was ~55 nm, and the lengths of the *p*-Ge, *i*-Si, and *n*-Si were ~2.5, ~1.6, and ~3.4  $\mu$ m, respectively. The length of each segment was estimated from the growth time and estimated growth rate of each respective segment; measurements of p-Ge segment after growth confirmed the estimation. Based on a previous work, the heterojunction width (i.e., the intermixed region) between the Ge and Si sections is estimated to be  $\sim 12-50$  nm, of the same order as the wire diameter.<sup>1</sup>

After growth, the wires were dispersed on a heavily doped p-type silicon substrate covered by ~100 nm of thermally grown SiO<sub>2</sub>. For TFET fabrication, hetero-NWs with a structural kink at the Ge/Si transition were preferentially chosen to precisely determine the junction position for top trigate placement. Contacts to the nanowires were made by e-beam lithography (EBL), followed by a 30 s diluted (1%) HF dip to remove the native oxide, the deposition of 100 nm of Ni metal, and lift-off. Trigate devices were fabricated by depositing 10 nm of high- $\kappa$  HfO<sub>2</sub> at 200 °C by atomic layer deposition (ALD), followed by a second EBL step and lift-off to define the metal gate on top of the *i*-Si section with an intentional overlap over the *p*-Ge/*i*-Si junction. Finally, the samples were annealed at 350 °C for 1 min in forming gas to improve the contact resistance through GeNi and SiNi silicide formation.

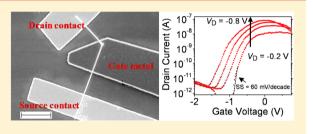

To confirm rectifying behavior and determine the doping level, four-contact geometry devices were made as shown in Figure 1a (the inset shows a fabricated top-gated device).  $I_{\rm D} - V_{\rm D}$  measurements of the devices show good rectification with forward to reverse current ratios up to 3 orders (Figure 1b). Fitting the  $I_{\rm D}(V_{\rm D})$  characteristic in forward bias with ideal diode model:

$$I_{\rm D} = I_0 [\exp(qV_{\rm D}/nkT) - 1] \tag{1}$$

we obtain an ideality factor  $n \sim 3$ , indicating that the dominant current-carrying mechanism in forward bias is generation and recombination.<sup>19</sup>

The doping type of Ge and Si sections was confirmed via backgate measurements. In this measurement a constant voltage was applied between contacts on the *p*-Ge and *n*-Si sections of the hetero-NW, with the current *I* monitored as a function of backgate voltage  $V_{BG}$  applied to the doped Si substrate and swept from -20 to 20 V. Transfer curves from such measurements are shown in upper inset of Figure 1b. The linear two-point I-V characteristics of the *p*-Ge and *n*-Si

**Figure 1.** (a) SEM image of four-contact geometry of the kinked Ge– Si hetero-NW prior to gate metal deposition; inset shows a fabricated top-gated device (scale bar is 2  $\mu$ m). (b)  $I_D-V_D$  rectification at T =300 K, with the dashed line indicating a  $n \sim 3$  ideality factor. Upper inset shows doping confirmation of *p*-Ge and *n*-Si sections via backgate  $V_{BG}$  response, lower inset showing two-point ohmic response of the n-n and p-p contacts at  $V_{BG} = 0$  V used to infer the doping level in the *p*-Ge and *n*-Si sections.

sections at  $V_{\rm BG} = 0$  V, shown in Figure 1b lower inset, confirm good ohmic contacts and make it possible to estimate the doping values.<sup>20</sup> Taking bulk *p*-Ge and *n*-Si mobilities and an unpassivated surface state density of  $5 \times 10^{12}$  cm<sup>-2</sup> in Ge<sup>21</sup> and  $2 \times 10^{12}$  cm<sup>-2</sup> in Si,<sup>22</sup> we estimate *p*-and *n*-doping levels to be ~2-3 × 10<sup>18</sup> cm<sup>-3</sup> and ~1-2 × 10<sup>18</sup> cm<sup>-3</sup>, respectively, although true doping densities may be higher since the real mobility in our narrow NW materials is likely lower than in the bulk.

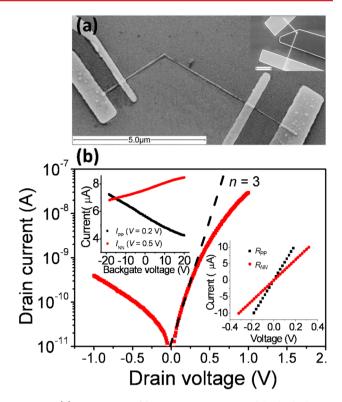

The operating principle of our Ge-Si hetero-NW TFETs is illustrated with the energy band diagram shown in Figure 2, calculated based on the expected composition and doping profile along the axis of our hetero-NWs.<sup>4</sup> In the TFET mode, Figure 2a, a negative drain voltage  $V_{\rm D}$  is applied to the p-Ge section with respect to the grounded n-Si source. The gate voltage V<sub>G</sub> modulates the intrinsic Si channel, as well as the electric field at the tunneling junction. In the off state, a negative  $V_{\rm G}$  pulls the channel conduction band up, shifting the high electric field to n-Si source-channel junction and suppressing BTBT due to the wide bandgap of Si (see Figure 2a). Conversely, positive  $V_{\rm G}$  lowers the *i*-Si channel's conduction band below the *p*-Ge valence band. The electric field at the drain-channel heterojunction, arising from a combination of  $V_{\rm G}$  and  $V_{\rm D}$ , promotes BTBT current from the Ge valence band in the drain to the *i*-Si conduction band, which is enhanced by the smaller Ge bandgap (see Figure 2b). The gate was positioned to extend over the *i*-Si channel into the *p*-Ge drain region (beyond the kink, see inset in Figure 1a), to

**Nano Letters**

**Figure 2.** (a, b) Energy band diagrams of the device in TFET mode, where  $V_D < 0$  and  $V_G$  modulates the tunneling current: (a) negative  $V_G$  shifts the high electric field to Si source-channel junction, where tunneling is limited, (b) positive  $V_G$  enables BTBT tunneling at the Ge–Si drain-channel heterojunction, turning on the device. (c)  $I_D - V_D$  output characteristics as a function of  $V_G = -2$  to 0 V in 0.5 V steps, showing gate control of  $I_D$ . (d)  $I_D - V_G$  transfer characteristics at  $V_D = -0.2$  to -0.8 V in 0.2 V steps. At  $V_G = 0.1$  V,  $I_{ON}$  reaches ~100 nA (~2  $\mu$ A/ $\mu$ m normalized to diameter). Dashed line indicates SS = 60 mV/decade.

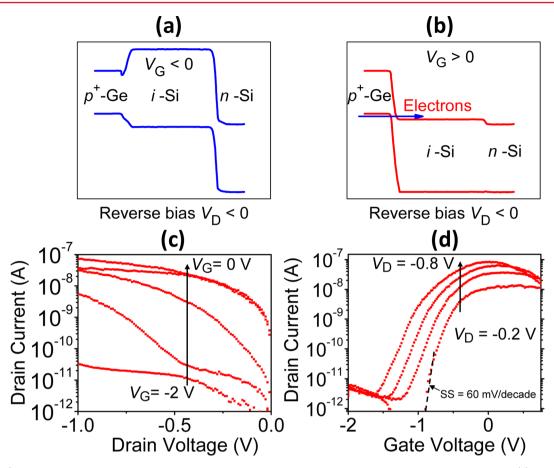

Figure 3. (a) 3D Sentaurus TCAD model and a 2D cut through the midpoint of the wire, with *p*-doped Ge shown as blue and *n*-doped Si as red, dashed line indicates the *p*-Ge/*i*-Si junction; (b) simulated  $I_D - V_G$  characteristics at  $V_D = -0.2$  to -0.8 V in 0.2 V steps, showing good agreement with experimental data.

ensure that the maximum electric field at positive gate voltage,  $E_{\rm MAX}$ , lies within the Ge section, maximizing tunneling current.<sup>23</sup> The shift in the tunneling junction between Ge and Si contributes to higher  $I_{\rm ON}$  current and suppressed  $I_{\rm OFF}$ .

Figure 2c shows  $I_D-V_D$  characteristics, measured from  $V_D = 0$  to -1 V at a fixed  $V_G = -2$  to 0 V in 0.5 V steps. At high positive  $V_G$ , the maximum electric field  $E_{MAX}$  at the tunneling heterojunction is largely determined by  $V_G$  and is only weakly dependent on  $V_D$ . At lower  $V_G$ , both  $V_G$  and  $V_D$  contribute to  $E_{MAX}$ , with  $I_D$  demonstrating nearly exponential dependence on

$V_{\rm D}$  (similar to the drain-induced barrier lowering or DIBL observed in short-channel MOSFETs). Figure 2d shows the  $I_{\rm D}-V_{\rm G}$  transfer characteristics of our device at constant  $V_{\rm D}$  = -0.2 to -0.8 V in 0.2 V steps. The maximum  $I_{\rm ON}$  achieved in our device at  $V_{\rm G}$  = 0.1 V and modest  $V_{\rm D}$  = -0.8 V is ~2  $\mu A/\mu m$  (normalized to the wire diameter), comparable to or higher than that reported for Si-based NW,<sup>24,25</sup> Ge-based,<sup>26</sup> Ge-SiGe core–shell NW,<sup>27</sup> and the recently reported axial InP-GaAs hetero-NW TFET.<sup>28</sup> At even higher  $V_{\rm G}$  > 0.1 V,  $I_{\rm D}$  begins to drop, as the gate voltage begins to deplete carriers in the *p*-Ge

**Nano Letters**

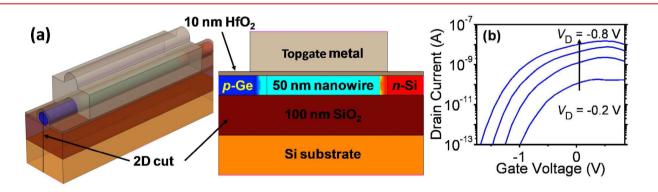

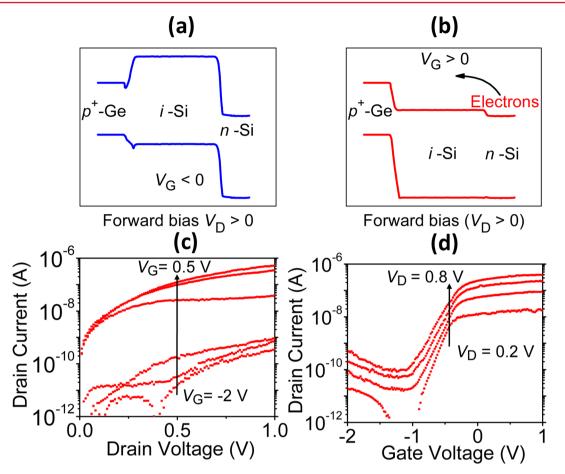

**Figure 4.** (a and b) Energy band diagram of the device in FET working mode where  $V_D > 0$  positive and  $V_G$  modulates thermal injection of carriers: (a) negative  $V_G$  increases the *i*-Si channel barrier, preventing thermal injection of carriers into channel; (b) positive  $V_G$  lowers the *i*-Si barrier, turning on the device; (c) experimental  $I_D - V_D$  at different  $V_G = -2$  to 0.5 V in 0.5 V steps; (d)  $I_D - V_G$  at positive  $V_D = 0.2$  to 0.8 V in 0.2 V steps.

section resulting in lower  $E_{\rm MAX}$  at the tunneling heterojunction. Due to our axial heterostructure, ambipolar behavior is suppressed with a very low  $I_{\rm OFF} \sim 10^{-12}$  Å (corresponding to  $I_{\rm OFF} \sim 20 \text{ pA}/\mu\text{m}$ ). The  $I_{\rm ON}/I_{\rm OFF}$  ratio of our devices is 5 decades of current, with an average subthreshold slope SS  $\sim$ 140 mV/decade over 4 orders. The best SS, observed over the two lowest decades of  $I_{D}$ , is ~50 mV/decade. Better device performance, meaning higher I<sub>ON</sub> and smaller SS, could be realized by improving the heterojunction abruptness,<sup>2</sup> surface passivation, better electrostatic gate control (gate all-around structure, possible in a vertical layout demonstrated recently for Si TFETs<sup>29,30</sup>), and increased drain doping. Further, the evidence of tunneling behavior in our TFETs is self-contained, without the possibility of explaining the transfer characteristics through conventional field-effects or Schottky barrier action, given the biasing scheme depicted in Figures 2a and b and the observed SS < 60 mV/decades at low  $I_D$ .

To validate the experimentally measured results, threedimensional (3D) TCAD simulations were performed using Synopsys Sentaurus. Figure 3a illustrates the simplified 3D structure of a nanowire TFET, comprised of a 100 nm thick and  $10^{17}$  cm<sup>-3</sup> *n*-doped Si layer, a 100 nm thick SiO<sub>2</sub> buried oxide, a straight cylindrical nanowire section of 50 nm diameter, a 10 nm thick HfO<sub>2</sub> top gate, and a nickel trigate metal. A crosssection down the midpoint of the cylindrical hetero-NW is also shown. The doping in the *p*-Ge drain and *n*-Si was taken as  $5 \times 10^{18}$  cm<sup>-3</sup>, and the extent of the source and drain regions was taken as 150 nm. The decay of the doping into the nominally undoped *i*-Si channel (assumed to be  $10^{15}$  cm<sup>-3</sup> *p*-Si) was taken as 6 nm per decade of doping, whereas the transition between Ge and Si was taken to occur linearly over 50 nm, in reasonable agreement with experimental measurement (see S1 in the Supporting Information). We have also carried out simulations for different transition slopes (over 30–70 nm) and find that the resulting change in maximum electric field does not qualitatively change the results here.

Letter

Figure 3b represents the simulated  $I_D - V_G$  curves for the structure of Figure 3a in TFET mode. The simulations confirmed that the current conduction is due to BTBT in the region around the SiGe transition region near the p-Ge drain boundary. The rate of BTBT was determined using dynamic nonlocal tunneling model, where the tunneling path is dynamically updated in each iteration to align with the gradient of the potential, crossing the bandgap from the conduction band into the valence band. Since it is known that high- $\kappa$ dielectric/semiconductor interface has a high trap density,<sup>31</sup> we assumed a positive fixed oxide charge of the density of 1.5  $\times$  $10^{13}$  cm<sup>-2</sup> at the high- $\kappa$  dielectric/SiGe interface, which effectively shifted the threshold voltage by ~1.5 V, similar to our experiment. The tunneling reduced mass for Ge, which is a fitting parameter of the BTBT model, was modified from the default value of  $m_r = 0.017m_0$  to  $0.01m_0$ .<sup>32</sup> With these assumptions, the simulation results in Figure 3b are in reasonable quantitative agreement with the data in Figure 2d, matching the experimentally measured  $I_{ON}$  values and subthreshold slopes, as well as the  $I_{\rm ON}/I_{\rm OFF}$  ratio of ~10<sup>5</sup>,

The benefits derived from bandgap engineering along the length of our hetero-NW device architecture not only apply to TFETs but also can be used for adding a built-in electric field in the channel of a conventional MOSFET, due to the Ge/Si  $\sim$ 0.6 eV valence band offset. This effect is shown here by operating our device in forward bias mode, where a positive  $V_{\rm D}$ is applied to the *p*-Ge drain with respect to the *n*-Si source, and  $V_{\rm G}$  controls the thermal injection of carriers into the channel. The energy band diagrams corresponding to this bias configuration are shown in Figure 4a and b. Because of the difference between Ge and Si bandgaps, a negative  $V_{\rm G}$  can push the conduction band of the *i*-Si channel above the conduction band of p-Ge drain, creating a barrier that effectively shuts down the thermal diffusion of electrons from the n-Si source to the *p*-Ge drain (Figure 4a). Conversely, a positive  $V_{\rm G}$  pulls the i-Si channel conduction band down below that of p-Ge drain, enabling carriers to freely diffuse from the source to the drain when a positive  $V_{\rm D}$  is applied (Figure 4b). This operating mode is experimentally verified in measurements shown in Figure 4c and d. In Figure 4c,  $I_{\rm D} - V_{\rm D}$  is shown as a function of  $V_{\rm G}$  in the -2 to 0.5 V range, whereas Figure 4d plots the  $I_D - V_G$  transfer characteristic as a function of  $V_{\rm D}$  = 0.2 to 0.8 V in 0.2 V steps. The device performance in this mode is, in fact, slightly less impressive than the TFET mode, with SS  $\sim$  150 mV/decade and  $I_{\rm ON}$  reaching ~0.5  $\mu A$  (corresponding to ~10  $\mu A/\mu m$ normalized to wire diameter). The higher  $I_{ON}$  in this operating mode is expected due to the fact that this mode requires no tunneling across a barrier for charge carriers to be emitted from the source to the channel, and transport is governed by driftdiffusion from the source to the drain. However, this mode of operation is fundamentally limited to SS of 60 mV/decade, whereas the TFET mode can overcome this diffusion-based limit.6,7

In conclusion, we have demonstrated the successful growth, fabrication, and characterization of axial *p*-Ge/*i*-Si/*n*-Si hetero-NW TFET. Our hetero-NWs were realized using the VLS method with better abruptness of axial modulation of doping and composition compared to earlier reports on NW TFETs. The trigated devices show good performance with  $I_{\rm ON}$  of up to  $\sim 2 \,\mu {\rm A}/\mu{\rm m}$  (normalized to the wire diameter) with suppressed ambipolar behavior and average SS of  $\sim 140 \, {\rm mV}/{\rm decade}$  (SS  $\sim 50 \, {\rm mV}/{\rm decade}$  over the lowest two decades of  $I_{\rm D}$ ), with a potential for further improvement. A 3D Sentaurus TCAD model simulation confirms the device working principle based on band-to-band tunneling at the heterojunction. Due to the Ge–Si heterojunction, our device can also operate as nanowire FET with improved transport characteristics at forward sourcedrain bias, with no interband tunneling.

## ASSOCIATED CONTENT

#### **S** Supporting Information

SiGe composition profiles, obtained from atom probe tomography (APT) analysis. This material is available free of charge via the Internet at http://pubs.acs.org.

# AUTHOR INFORMATION

#### Corresponding Author

\*E-mail: son\_le@brown.edu (S.T.L.); alexander\_zaslavsky@ brown.edu (A.Z.).

#### Notes

The authors declare no competing financial interest.

# ACKNOWLEDGMENTS

The work at Brown was supported by the NSF (awards ECCS-1068895 and DMR-1203186). Heteronanowire epitaxy was performed at the Center for Integrated Nanotechnologies, a U.S. Department of Energy, Office of Basic Energy Sciences user facility at Los Alamos National Laboratory (Contract DE-AC52-06NA25396) and Sandia National Laboratories (Contract DE-AC04-94AL85000), and the work was supported in part by the LANL LDRD program. A portion of the research was performed using EMSL, a national scientific user facility sponsored by the Department of Energy's Office of Biological and Environmental Research and located at Pacific Northwest National Laboratory. The authors would like to thank Brown's Center for Computation and Visualization for making the Oscar cluster available for device simulations. We would like to thank Dr. Aditya Mohite, CINT-LANL for useful discussions and advises on device fabrication throughout the project.

### REFERENCES

(1) Perea, D. E.; Li, N.; Dickerson, R. M.; Misra, A.; Picraux, S. T. Controlling heterojunction abruptness in VLS-grown semiconductor nanowires via in situ catalyst alloying. *Nano Lett.* **2011**, *11*, 3117.

(2) Wen, C.-Y.; Reuter, M. C.; Bruley, J.; Tersoff, S.; Kodambaka, S.; Stach, E. A.; Ross, F. M. Formation of compositionally abrupt axial heterojunction in silicon-germanium nanowires. *Science* **2009**, *326*, 1247.

(3) Lensch-Falk, J. L.; Hemesath, E. R.; Perea, D. E.; Lauhon, L. J. Alternative catalysts for VSS growth of silicon and germanium nanowires. *J. Mater. Chem.* **2009**, *19*, 849.

(4) Perea, D. E.; Schreiber, D. K.; Devaraj, A.; Thevuthasan, T.; Yoo, J.; Dayeh, S. A.; Picraux, S. T. Controlling axial p-n heterojunction abruptness through catalyst alloying in vapor-liquid-solid grown semiconductor nanowires (Poster Abstract). *Microscopy and Microanalysis Conference*, Phoenix, AZ, USA; Jul. 29 - Aug. 2, 2012.

(5) Appenzeller, J.; Knoch, J.; Björk, M. T.; Riel, H.; Schmid, H.; Riess, W. Toward nanowire electronics. *IEEE Trans. Electron Dev.* 2008, 55, 11.

(6) Seabaugh, A. C.; Zhang, Q. Low-voltage tunnel transistors for beyond CMOS logic. *Proc. IEEE* **2010**, *98*, 2095.

(7) Ionescu, A.; Riel, H. Tunnel field effect transistors as energy efficient electronic switches. *Nature* **2011**, 479, 329.

(8) Choi, W. Y.; Park, B.-G.; Lee, J. D.; Liu, T.-J. K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. *IEEE Electron. Dev. Lett.* **2007**, *28*, 8.

(9) Mayer, F.; Le Royer, C.; Damlencourt, J.-F.; Romanjek, K.; Andrieu, F.; Tabone, C.; Previtali, B.; Deleonibus, S. Impact of SOI,  $Si_{1-x}Ge_xOI$  and GeOI substrates on CMOS compatible tunnel FET performance. *Tech. Dig. IEDM* **2008**, 163–166.

(10) Sze, S. M. Physics of Semiconductor Devices, 2nd ed.; Wiley: New York, 1981.

(11) Kazazis, D.; Jannaty, P.; Zaslavsky, A.; Le Royer, C.; Tabone, C.; Clavelier, L.; Cristoloveanu, S. Tunneling field-effect transistor with epitaxial junction in thin germanium-on-insulator. *Appl. Phys. Lett.* **2009**, *94*, 263508.

(12) Dayeh, S. A.; Picraux, S. T. Axial Ge/Si heterostructure tunnel FETs. *ECS Trans.* **2010**, *33*, 373.

(13) Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. C. Double gate strained-Ge heterostructure tunneling FET (TFET) with record high drive current and < 60 mV/dec subthreshold slope. *IEDM Tech. Dig.* **2008**, 947.

(14) Aydin, C.; Zaslavsky, A.; Luryi, S.; Cristoloveanu, S.; Mariolle, D.; Fraboulet, D.; Deleonibus, S. Lateral interband tunneling transistor in silicon-on-insulator. *Appl. Phys. Lett.* **2004**, *84*, 1780.

(15) Wan, J.; Le Royer, C.; Zaslavsky, A.; Cristoloveanu, S. Tunneling FETs on SOI: Suppression of ambipolar leakage, low-frequency noise behavior, and modeling. *Solid-State Electron.* **2009**, 65–66, 226.

(16) Dayeh, S. A.; Dickerson, R. M.; Picraux, S. T. Axial bandgap engineering in germanium-silicon heterostructured nanowires. *Appl. Phys. Lett.* **2011**, *99*, 113105.

(17) Dayeh, S. A.; Picraux, S. T. Axial Ge/Si nanowire heterostructure tunnel FETs. *Electron. Chem. Soc. Trans.* 2010, 33, 373.

(18) Dayeh, S. A.; Wang, J.; Li, N.; Huang, J. Y.; Gin, A. V.; Picraux, S. T. Growth, Defect Formation and Morphology Control of Germanium-Silicon Semiconductor Nanowire Heterostructures. *Nano Lett.* **2011**, *11*, 4200.

(19) Leonard, F.; Talin, A. A.; Swartzentruber, B. S.; Picraux, S. T. Diameter dependent electronic transport properties of Au-catalyst/Ge nanowire Schottky diodes. *Phys. Rev. Lett.* **2009**, *102*, 106805.

(20) Le, Son, T.; Jannaty, P.; Zaslavsky, A.; Dayeh, S. A.; Picraux, S. T. Growth, electrical rectification, and gate control in axial *in situ* doped p-n junction germanium nanowires. *Appl. Phys. Lett.* **2010**, *96*, 262102.

(21) Dimoulas, A.; Tsipas, P. Germanium surface and interfaces. *Microelectron. Eng.* **2009**, *86*, 1577.

(22) Park, J. T.; Kim, J. Y.; Islam, M. S. Extraction of doping concentration and interface state density in silicon nanowire. *IEEE Trans. Nanotechnol.* **2011**, *10*, 5.

(23) Verhulst, A. S.; Vandenberghe, W. G.; Maex, K.; Groeseneken, G. Tunnel field-effect transistor without gate-drain overlap. *Appl. Phys. Lett.* **2007**, *91*, 053102.

(24) Björk, M. T.; Knoch, J.; Schmid, H.; Riel, H.; Riess, W. Silicon nanowire tunneling field-effect transistors. *Appl. Phys. Lett.* **2008**, *92*, 193504.

(25) Vallett, A. L.; Minassian, S.; Kaszuba, K. P.; Datta, S.; Redwing, J. M.; Mayer, T. S. Fabrication and characterization of axially doped silicon nanowire tunnel field-effect transistors. *Nano Lett.* **2010**, *10*, 4813.

(26) Kim, S. H.; Kam, H.; Hu, C.; Liu, T.-J. K. Germanium source tunnel field effect transistors with record high  $I_{\rm ON}/I_{\rm OFF}$ . VLSI Symp. Tech. Dig. 2009, 1, 178.

(27) Nah, J.; Liu, E.-S.; Varahramyan, K. M.; Tutuc, E. Ge-Si<sub>x</sub>Ge<sub>1-x</sub> core-shell nanowire tunneling field effect transistors. *IEEE Trans. Electron Devices* **2010**, *57*, 8.

(28) Ganjipour, B.; Wallentin, J.; Borgström, M. T.; Samuelson, L.; Thelander, C. Tunnel field-effect transistors based on InP-GaAs heterostructure nanowires. *ACS Nano* **2012**, *6*, 3109.

(29) Vandooren, A.; Leonelli, D.; Rooyackers, R.; Arstila, K.; Groeseneken, G.; Huyghebaert, C. Electrical results of vertical Si n-tunnel FETs. *Proc. ESSDERC* **2011**, 255–8.

(30) Gandhi, R.; Chen, Z.; Singh, N.; Banerjee, K.; Lee, S. CMOScompatible vertical-silicon-nanowire gate-all-around p-type tunneling FETs with  $\leq$  50-mV/decade subthreshold swing. *IEEE Electron Device Lett.* **2011**, *32*, 11.

(31) Zafar, S.; Kumar, A.; Gusev, E.; Cartier, E. Threshold voltage instabilities in high- $\kappa$  gate dielectric stacks. *IEEE Trans. Dev. Mater. Reliab.* **2005**, *5*, 45.

(32) Hellings, G.; Eneman, G.; Krom, R.; Jaeger, B. D.; Mitard, J.; Keersgieter, A. D.; Hoffmann, T.; Meuris, M.; Meyer, K. D. Electrical TCAD simulations of a germanium pMOSFET technology. *IEEE Trans. Electron Devices* **2010**, *57*, 10.